- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT82V3202NLG (IDT, Integrated Device Technology Inc)IC PLL WAN EBU SGL 68-VFQFPN

IDT82V3202

EBU WAN PLL

Functional Description

26

September 11, 2009

The phase lock alarm can be cleared by the following two ways, as

selected by the PH_ALARM_TIMEOUT bit:

Be cleared when a ‘1’ is written to the corresponding

INn_CMOS_PH_LOCK_ALARM bit;

Be cleared after the period (= TIME_OUT_VALUE[5:0] X

MULTI_FACTOR[1:0] in second) which starts from when the

alarm is raised.

The selected input clock with a phase lock alarm is disqualified for T0

DPLL locking.

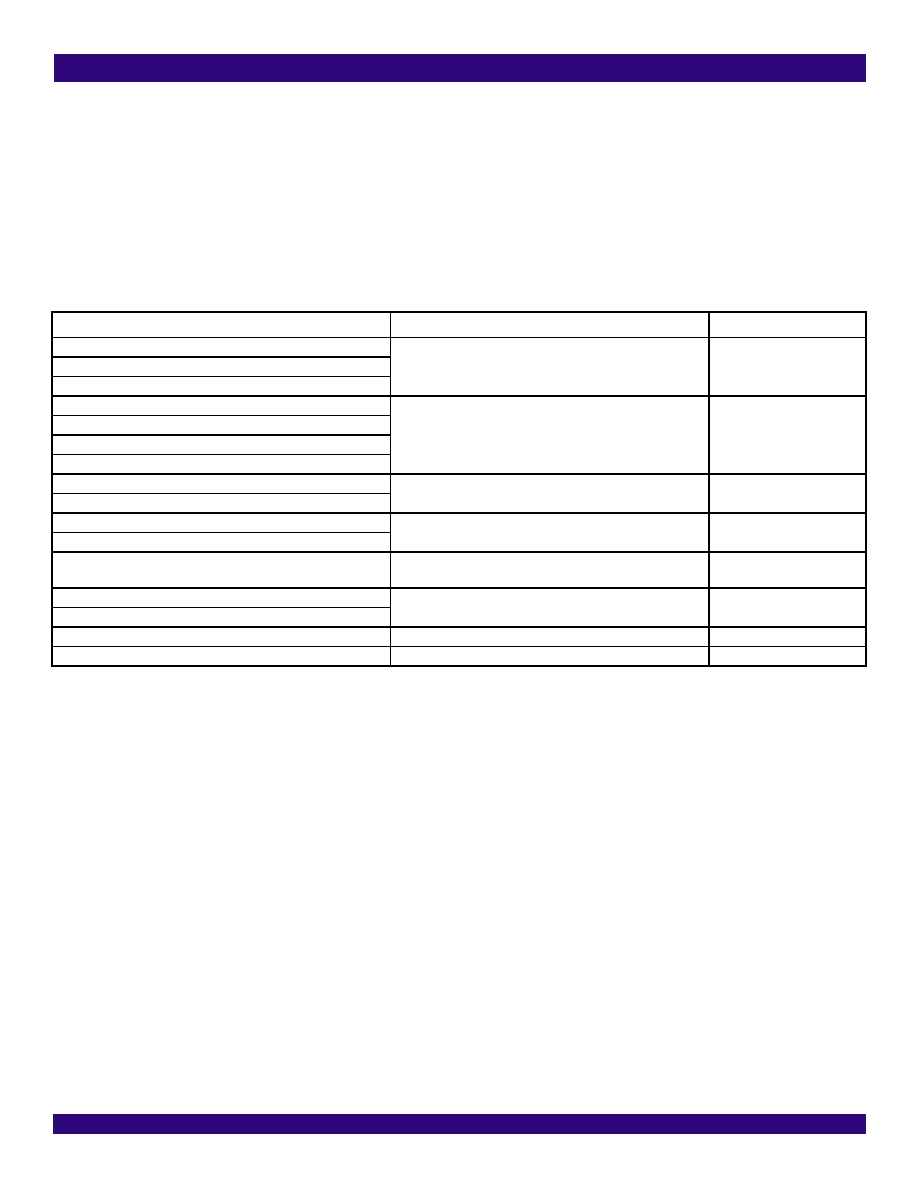

Table 12: Related Bit / Register in Chapter 3.7

Bit

Register

Address (Hex)

FAST_LOS_SW

PHASE_LOSS_FINE_LIMIT_CNFG

5B

PH_LOS_FINE_LIMT[2:0]

FINE_PH_LOS_LIMT_EN

MULTI_PH_8K_4K_2K_EN

PHASE_LOSS_COARSE_LIMIT_CNFG

5A

WIDE_EN

PH_LOS_COARSE_LIMT[3:0]

COARSE_PH_LOS_LIMT_EN

T0_DPLL_SOFT_FREQ_ALARM

OPERATING_STS

52

T0_DPLL_LOCK

DPLL_FREQ_SOFT_LIMT[6:0]

DPLL_FREQ_SOFT_LIMIT_CNFG

65

FREQ_LIMT_PH_LOS

DPLL_FREQ_HARD_LIMT[15:0]

DPLL_FREQ_HARD_LIMIT[15:8]_CNFG,

DPLL_FREQ_HARD_LIMIT[7:0]_CNFG

67, 66

TIME_OUT_VALUE[5:0]

PHASE_ALARM_TIME_OUT_CNFG

08

MULTI_FACTOR[1:0]

INn_CMOS_PH_LOCK_ALARM (n = 1 or 2)

IN1_IN2_CMOS_STS

44

PH_ALARM_TIMEOUT

INPUT_MODE_CNFG

09

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT82V3255TFG

IC PLL WAN SMC STRATUM 3 64-TQFP

IDT82V3280APFG

IC PLL WAN SE STRATUM 2 100TQFP

IDT82V3285AEQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3285EQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3288BCG

IC PLL WAN 3E STRATUM 2 208CABGA

IDT82V3355EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3358EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDTCSPT857DNLG8

IC PLL CLK DVR SDRAM 40-VFQFPN

相关代理商/技术参数

IDT82V3202NLG8

功能描述:IC PLL WAN EBU SGL 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3202NLGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:EBU WAN PLL

IDT82V3255

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255_08

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255DK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255DKG

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255DKG8

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255EDGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL